|

AG32的时钟输入种类● 内部HSI: AG32有内置的HSI时钟:8Mhz。 但是这个时钟偏差比较大,个别甚至接近10Mhz。这个时钟对于有时序要求的接口,如UART,USB等是无法接受的。为了改善这个时钟,AGM做了一个内部时钟校准,利用下载器的时钟来校准,然后存在内部flash中。 校准后的精度可以在1%以内。

AGM的串口启动,是没有用到外部时钟的,因为ROM代码本身也不知道系统外部时钟是多少。串口启动是通过接收PC发送的固定字节来校准时钟的,PC发送的0x7F。代码通过起始位和最后1bit的低电平来校准。因此,ROM代码是不关心下载波特率的。

下载器是通过USB通讯的,也用了类似的校准方法,通过usb 1mS中断信号来实现的。因此,下载器上如果没有外部晶体也没关系。但是,下载器多了一个离线下载功能,这个需要用到外部时钟。

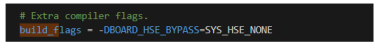

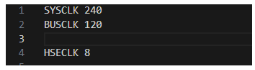

VE 里定义如下:

由于没有用到HSE那部分电路,因此ini里需要添加宏定义: BOARD_HSE_BYPASS=SYS_HSE_NONE

同时还有一点限制,逻辑部分要压缩,这一点容易忽略。 platformio.ini 中配置board_logic.compress = true

● 外部无源时钟HSE: 无源时钟通过OSC_IN, OSC_OUT 接入,4~26MHz,一般推荐的是8Mhz。 用户根据自己需要的时钟,适当调整外部晶体的频率。

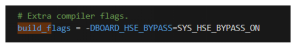

VE 里如下定义即可:

其实,ini里需要定义 BOARD_HSE_BYPASS=SYS_HSE_BYPASS_OFF,但是因为这个是默认项,可以不定义。

● 外部有源晶振HSE: 从OSC_IN 输入 这个与无源晶体的区别就是不需要谐振电路了,因此增加SYS_HSE_BYPASS_ON的定义。 即BYPASS掉谐振电路

VE配置同无源晶体一样。

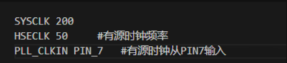

● 从其它引脚输入 如果是纯CPLD应用,那就只能用有源晶振,从全局时钟(带GB标志)处输入。 其它引脚一般不建议接入有源时钟。 同样,这个没有HSE部分,需要定义SYS_HSE_NONE。INI里配置同HSI。

VE配置如下:

如果AG32是通过系统中的其它MCU来给其提供时钟的话,参照有源时钟的输入方法定义。 需要获取更多的“资料”和“支持”和“样片测样申请”可以联系我们 提供“芯片测样-发送资料-技术支持-批量采购” 联系方式: 姚工 13661545024(VX同号) (加的时候备注下公司名和个人名字) 在线商城:agm-micro.taobao.com 公司网站:www.agm-micro.com 资料网站: www.tcx-micro.com |